# 通信·信号処理技術をチップ内/間高速高効率情報伝送に利用した 集積回路システムの構築

弓 仲 康 史 群馬大学大学院工学研究科准教授

#### 1 目的

VLSI システムの極限微細化・高速化に伴い、Gbps オーダの高速な信号伝送技術、さらに複数の機能チップを積層した 3 次元 LSI 技術がシステムの高性能化に不可欠な技術となっている。現在、MPU チップ等では、Gbps オーダの高速信号が内部信号として用いられているが、メモリおよび他のチップとのインタフェースではプリント基板や配線を介しての情報伝送となり、基板、配線等の伝送媒体の抵抗、容量成分に起因する波形劣化のため、伝送速度が大幅に律速されているのが現状である。具体的には、伝送路中の寄生素子 (R(抵抗)、L(インダクタ)、C(容量) 成分等) に起因する帯域制限の影響により高周波成分が失われ、連続する信号が互いに干渉する符号間干渉の影響のため、原信号の情報が忠実に再現できず、誤動作を引き起こす問題が深刻となっている。

これに対して、通信の分野で利用されている波形整形・等化(イコライズ)等の信号処理技術を集積回路システムの信号伝送へ適用し、波形を整形することにより信号の高速伝送を可能とする高速インタフェース技術が、LSI の高性能化に必要不可欠となりつつある。また、多レベル信号を用いた高性能インタフェース技術の導入も注目されている。例えば、4値信号は2ビットの情報を1シンボルとして同時に伝送できるため、同じデータ量を伝送する場合、2値と比較して半分のデータレートで情報伝送可能である。すなわち、4値伝送を採用することにより、信号のデータレートを半分とすることが可能であるため、伝送路の帯域制限の影響を軽減できると共に、送受信ドライバ回路の動作周波数を下げることができ、消費電力の低減が実現できる。これまでに、帯域の拡張により、10Gbps 程度の高速信号伝送を可能とする CMOS イコライズ回路が提案されている。しかしながら、これらは主に2値信号の波形整形を対象としたものであり、多レベル信号を対象とした波形整形技術の提案、検討はほとんどなされていないのが現状である。

また、チップ間信号伝送の速度向上にはチップ間の配線長を削減し、寄生抵抗、寄生容量を減らすことも効果的である。配線長を削減する VLSI システムの実装技術として、SoC(System on Chip)や SiP(System in Package)が開発されている。SoC とは 1 チップ上に VLSI システムを構成する実装技術であり、通信距離を大幅に削減でき、高速な通信を可能とする。しかし、製造コストが高く、開発時間も長くなるといった問題がある。これらの問題を解決するために、1 つのパッケージの中に複数のチップを組み合わせ、チップを 3 次元積層することで VLSI システムを構成する SiP 技術が提案されている。チップを専用プロセスで個別に製造できるためコストの削減、開発効率の向上が可能である。また、チップを 3 次元積層実装することで配線長を減らし、高速信号伝送、小型化、メモリの大容量化も可能である。以上のような理由により、現在 SiP が注目されている。 従来の SiP のチップ間インタフェースには有線で通信するワイヤボンディング、マイクロバンプ、貫通ビアなどがある。しかし、ワイヤボンディングでは伝送速度、マイクロバンプでは 3 層以上のチップへの通信、貫通ビアではコストが問題となる。

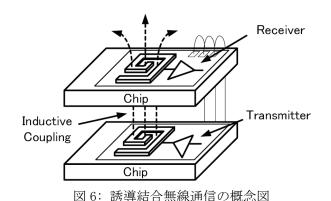

これらの問題を解決するために、近年、インダクタの誘導結合を用いた無線インタフェース技術が提案されている。本技術を用いることにより高速信号伝送、3層以上のチップへの信号伝送が可能である。さらに、通常の CMOS LSI 製造プロセスで実現できるため低コスト化が可能である。

以上のような観点から本研究課題では、通信・信号処理技術をチップ内/間高速高効率情報伝送に利用した 集積回路システムの構築を検討する。まず、ディジタル波形(2 値信号伝送)における種々の等化技術を検討 し、波形整形の効果をシミュレーション、原理実験で実証する。さらに、それらの等化技術の多値信号波形 整形への適用を検討する。次に、誘導結合を用いたチップ間無線インタフェースのさらなる高速高効率化を 目的とし、誘導結合無線通信への多値信号伝送の導入を検討する。

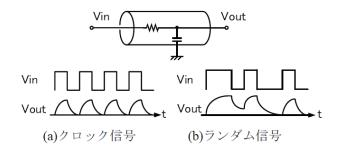

図1: 帯域制限された伝送路による波形の劣化

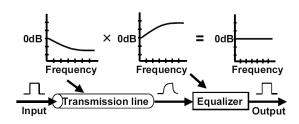

図3:波形等化の原理

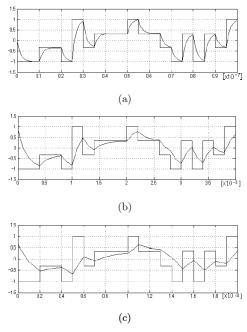

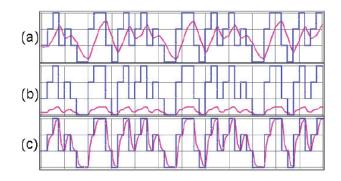

図 2: 100MHz に帯域制限された伝送路における 4 値信号の符号間干渉(ISI) の例 (a) 200Msps、(b) 500Msps、(c) 1Gsps

## 2 高速信号伝送における問題点

インピーダンス整合がなされたチップ/ボード間にディジタル波形を伝送する際、伝送路に十分な帯域(ディジタル波形の矩形波基本波成分と高次の高調波成分を含む)がある場合、原信号とほぼ同様の波形が受信可能である。これに対して、伝送する信号が高速化すると、伝送路中の寄生素子(R、L、C成分等)が顕在化する。すなわち、伝送路がローパスフィルタ特性を呈し、高調波成分が減衰するため、図 1(a)のように原信号が忠実に再現できなくなり、伝送可能なデータ速度が制限される。特に、図 1(b)に示すようなランダムなデータパターンの場合、パルス応答が「尾を引く」ため、次の信号検出タイミングまでに波形が整定せず、Low(0)または High(1)の判別が困難となる。このような現象は符号間干渉(Inter-SymbolInterference: ISI)と呼ばれており、ノイズマージンの低下を引き起こすと共に、動作周波数の上限を決定する要因の一つとなっている。

さらに、ISI の影響は 2 値信号と比較し、多値信号伝送時において顕著となる。図 2 は、帯域 100MHz の 伝送路に 200Msps、500Msps、16sps の 4 値信号を伝送した波形の Matlab シミュレーション結果である。ここで、sps [symbols per second] は、1 秒間に伝送可能な多値シンボルのデータ数の単位と定義する(2 値における bps [bits per second] に対応する)。Low beta bps [bits per second] に対応する)。Low beta bps bps

このように、多値信号伝送は、ISI およびノイズマージンの観点から 2 値信号伝送と比較し一見すると不利になると思われる。しかしながら、4 値信号は 2 ビットの情報を 1 シンボルとして同時に伝送できるため、同じデータ量を伝送する場合、2 値と比較して半分のデータレートで情報伝送可能である。すなわち、4 値伝送を採用することにより、信号のデータレートを半分とすることが可能であるため、伝送路の帯域制限の影響を軽減できると共に、送受信ドライバ回路の動作周波数を下げることができ、消費電力の低減が実現できる。現在、インタフェース技術において、多値伝送が着目されているのは、動作周波数を等価的に下げることにより、回路の設計制約を緩和可能であることを利用したものであり、このような概念は、今後の多値情報処理の適用分野の方向性を示唆するものと考えられる。

以下では、伝送路における波形劣化問題の解決を目的として、波形整形等の信号処理・回路技術に関する検討を行う。まず、等化技術の原理を概観し、最初にディジタル波形(2 値信号伝送)における種々の波形整形回路の動作原理を検討すると共に、波形整形の効果をシミュレーション、原理実験で実証する。次に、各等化技術を多値信号波形整形へ適用し、比較検討を行う。最後に、近年提案されている誘導結合を用いたチップ間無線インタフェースと波形整形技術を融合した誘導結合無線通信への多値信号伝送技術を検討する。

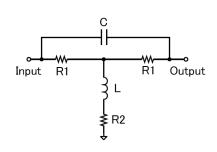

図 4: 連続時間型パッシブ イコライザの構成例

図 5:連続時間型パッシブイコライザのシミュレーション: (a)1.4GHz 帯域制限下において 8Gsps 相当の 4 値信号を伝送した場合の劣化波形、(b)パッシブイコライザ出力(約 1/6 にゲインが低下している)、(c) 出力を 6 倍にスケーリングした場合の出力

#### 3 等化回路の原理

伝送路の帯域制限に起因する波形劣化を補正する技術として、等化技術のインタフェース技術への適用が近年注目されている。等化(イコライズ)とは、周波数特性を変化させて波形を補正・整形する技術であり、主に通信の分野で古くから実用化されている手法である。これらの信号処理技術を集積回路システムの信号伝送へ適用することにより、伝送可能な信号の高速化を図る。一般に、無線信号における信号整形処理は動的に変化する無線伝送路に適応するために複雑な回路構成が要求される。これに対して、集積回路システムでは、配線の伝送路は分布定数回路等の簡易なモデルで表現され、RCローパスフィルタ特性等で近似できるため、等化回路の規模を大幅に削減可能である。

例えば、伝送路が図3に示すようなローパスフィルタ特性(積分特性)で近似できる場合、ハイパスフィルタ特性(微分特性)を有する等化回路を伝送路後に適用することにより、系全体の伝達関数をフラットにし、入力信号の波形を再現可能となる。このようなディジタル波形の整形を目的とした等化回路は種々提案されており、それぞれに利点欠点を有する。動作モードにより、離散時間型と連続時間型に分類され、さらに連続時間型はアクティブタイプ、パッシブタイプが提案されている。以下では、高速動作を目的とし、連続時間型イコライザの各々の動作原理と特徴を検討する。さらに、これらの等化回路を利用し、多値信号の整形を行ったシミュレーション結果を示す。

#### 3.1 連続時間型アクティブイコライザ

伝送路で失われた高周波成分をハイパスフィルタ動作により強調する原理の連続時間型のアクティブイコライザが種々提案されており、波形整形に有効であることが実証されている。しかしながら、一般に、数 GHz を越えるカットオフ周波数を有する高域強調フィルタ(ハイパスフィルタ)の実現は困難であると考えられる。従って、回路の低域のゲインを低下させ、等価的に高域のゲインを強調するハイパス周波数特性を実現する回路構成が主流である。本回路は MOS 差動対の間に R、C 素子を挿入した構成となっており、RC 値を変化させることにより低域のゲインおよびカットオフ周波数を調整可能である。

#### 3.2 連続時間型パッシブイコライザ

前節のアクティブイコライザは MOS トランジスタ構成のゲイン段自身の周波数特性により高域の特性が劣化するため、イコライズ可能な周波数が制限される。また、MOS トランジスタの消費電力等も問題となる。このような観点から、低消費電力かつ、帯域をさらに伸ばすことが可能なイコライズ回路の実現法として、連続時間型パッシブイコライザの構成を検討した。

図4に連続時間型パッシブイコライザの構成例を示す。抵抗3本からなるディバイダ回路にLとCを付加することにより、周波数特性を持たせ、低域のゲインを調整可能とするものである。MOSトランジスタ等のアクティブ素子や電源が不要であるため、帯域の拡大および低消費電力化が実現できる。抵抗R2を変化させることにより、低域のゲインを調整可能である。この抵抗R2をMOS抵抗で実現し、符号間干渉量のモニタ回路を用いてゲート電圧を変化させることにより、伝送線路に応じて特性をアダプティブに変化可能なイコ

ライズ特性を実現することも可能である。

#### 4 誘導結合無線通信

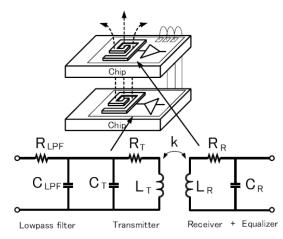

近年、SiP における柔軟な3次元配線の実現を目的として、インダクタの誘導結合を利用したチップ間無線インタフェース技術が提案されている。図6に誘導結合無線インタフェースの概念図を示す。インダクタを形成したチップを3次元積層し、近接したインダクタの誘導結合によって無線通信を行う。以下ではインダクタを用いたチップ間無線通信の原理を示し、その応用として、等化回路との一体化、多値信号伝送への拡張を検討する。

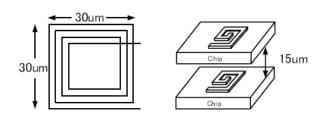

図7: インダクタのサイズと通信距離

#### 4.1 インダクタによる誘導結合

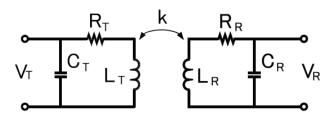

隣接するインダクタ間の誘導結合は次式で表される。

$$V_R = k\sqrt{L_T L_R} \frac{dI_T}{dt} \tag{1}$$

kは結合係数、 $L_{T}$ 、 $L_{R}$ は自己インダクタンスである。式(1)より受信インダクタの両端に発生する電圧  $V_{R}$ は、送信インダクタに流れる電流  $I_{T}$ の時間微分で与えられる。この誘導結合を利用してチップ間無線通信を行う。チップ間無線通信シミュレーションに用いるインダクタは図7のような直径  $30\,\mu$  m、チップ間の通信距離  $15\,\mu$  m とした。送信インダクタは大きな電流を流すために線幅を広く、巻数を少なくしている。一方、受信インダクタは自己インダクタンスを大きくするために線幅を狭く、巻数を多くしている。また、インダクタには寄生抵抗、寄生容量が存在する。それらを考慮したインダクタの等価回路は図8のようになる。この等価回路より、インダクタを用いた誘導結合の伝達関数は

図8: 寄生抵抗、寄生容量を考慮したインダクタの等価回路

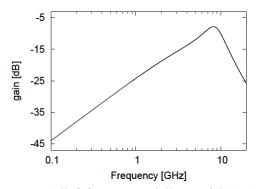

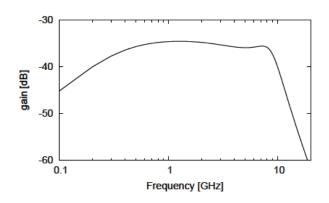

図 9: 誘導結合システム全体の周波数特性

$$\frac{V_R}{V_T} = \frac{j\omega\sqrt{L_T L_R}}{(R_T + j\omega L_T)(1 - \omega^2 L_R C_R + j\omega R_R C_R)}$$

(2)

となる。送信インダクタと受信インダクタのそれぞれのパラメータは巻数が 3 と 4、線幅が 1  $\mu$  m と 0.5  $\mu$  m、L、R、C 値がそれぞれ、4.4 nH、32 fF、100  $\Omega$  および 9 nH、38 fF、252  $\Omega$  とした。これらの値を用いた誘導結合全体の周波数特性は図 9 のようになり、バンドパスフィルタとして動作することがわかる。本パラメータを用いた場合、バンドパスフィルタの中心周波数(fc) は 8.6 GHz となる。

#### 4.2 誘導結合無線通信

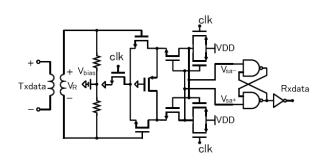

図 10:誘導結合無線通信の送受信回路

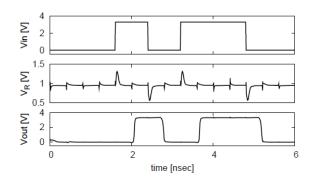

図 11: 誘導結合無線通信の送受信波形

図 10 に誘導結合無線通信の原理と回路構成を示す。まず、2 値信号 (0, 1) の遷移を正負の2 極性パルス電流に変換し、送信インダクタに流す。するとインダクタの誘導結合により受信側のインダクタに図 11 に示すようなパルス電圧  $V_R$  が発生する。このパルス電圧をセンスアンプと呼ばれる図 10 の増幅回路でクロックタイミング毎にサンプリングし、増幅する。センスアンプで増幅した信号を RSFF (Reset Set Flip-Flop) に入力することで 2 値信号を復元する。この方法によりチップ間伝送速度 1.5 Gbps の誘導結合無線通信を実現している。しかし、この回路構成では受信パルスの極性によって 0 か 1 を検出するため、センスアンプの動作速度に制約された 2 値信号しか伝送することができない。そこで、本研究課題では伝送速度の向上を目的とし、多値信号伝送を用いたチップ間無線通信技術を提案する。

図 13: イコライズ技術を用いた多値信号 伝送の概要

図 14: 平坦化された周波数特性

#### 4.3 イコライズ技術を用いた多値信号無線伝送

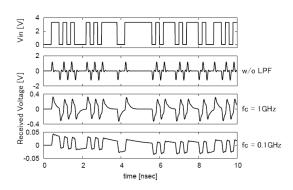

本方式は誘導結合の微分特性をイコライザとして利用し、誘導結合の周波数特性を平坦化することによって多値信号無線伝送を可能にする方式である(図 13)。誘導結合は式(1)のように微分特性を持つ。そのため、誘導結合はチップ間の無線通信としてだけでなく、イコライザとしても利用できる。誘導結合の微分特性を打ち消すために、送信インダクタの前にローパスフィルタ(積分特性)を挿入することで、図 14 のように誘導結合システム全体の周波数特性を平坦化する。平坦化された周波数内の帯域を持つ信号であれば、送信信号と同じ波形を受信インダクタから取り出せる。図 15 にローパスフィルタの遮断周波数を変化させた場合の受信波形を示す。図 15 上からそれぞれ、元波形、LPF なし、1GHz、0.1GHz のカットオフ周波数のフィルタを用いた場合の出力波形に対応する。ローパスフィルタの遮断周波数を高く設定した場合、大きな振幅は得られるが、波形が劣化してしまう。また、低い遮断周波数に設定した場合、波形の劣化は少なくなるが、振幅が小さくなる。つまり、波形形状と振幅はトレードオフの関係にある。そのため、シミュレーションにより波形形状と振幅が最適になるよう、ローパスフィルタの遮断周波数を決定した。

この方法は、イコライズ技術により、誘導結合の周波数特性を平坦化させることによって通信を行っている。そのため、平坦化された周波数特性が信号の帯域に対して十分であれば、多値信号でも伝送が可能である。さらに、隣接したインダクタを無線通信と波形等化のために同時に利用することにより、センスアンプを不要とし、回路規模を大幅に削減可能としている。しかしながら、本方式はパッシブイコライザ動作となるため、出力信号の振幅が低下し、多値レベルの判別が困難になるという問題があった。本研究では、多値レベルの判定を容易にするために、イコライザ出力を増幅する回路技術を新たに検討した。

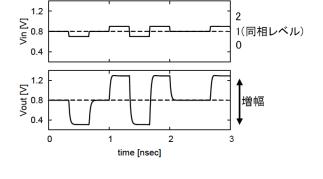

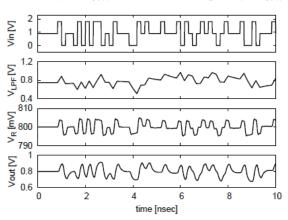

ここで、2 値信号(0、1) の場合は、gnd と Vdd レベルに出力をフルスイングに増幅するリミッタアンプ動作により信号レベルを増幅することが可能である。しかしながら、3 レベルの信号(0、1、2)を用いる場合、リミッタアンプ動作を行うと中間レベルを正しく再現することが困難となる。 そこで、本研究では、差動増幅回路に着目し、3 レベル(0、1、2) の中間レベル(1) を同相信号レベルとすることにより、正しく 3 レベルを増幅可能とする手法を新たに提案する(図 16)。より増幅率を大きくするために、図 17 のように増幅回路を多段接続した。図 18 に差動増幅回路の動作波形を示す。ローパスフィルタによって劣化した波形が誘導結合で無線通信されると、微分特性により受信波形がイコライズされ元の波形に戻る。その信号を差動増幅回路によって増幅する。この方法により、8mVp-p の信号を 158mVp-p に増幅し、3 値信号での伝送速度 6Gspsを実現した。

図 15:入力波形と LPF の遮断周波数を変化 させた場合の出力波形

図 16: 差動増幅回路を用いた 3 値信号の増幅

図 17: 3 値信号の増幅回路

図 18: イコライズ技術を用いた多値信号無線 伝送の波形: 上から入力波形、LPF 出力波形、 インダクタ受信波形、差動増幅回路出力波形

#### 5 まとめ

本研究課題では、通信・信号処理技術をチップ内/間高速高効率情報伝送に利用した集積回路システムの構築を検討した。まず、種々の等化技術を検討し、波形整形の効果をシミュレーション、原理実験で実証した。 さらに、それらの等化技術の多値信号波形整形への適用を検討した。次に、誘導結合を用いたチップ間無線インタフェースのさらなる高速高効率化を目的とし、誘導結合無線通信への多値信号伝送の導入を検討した。

### 【参考文献】

- [1] Y. Yuminaka and K. Yamamura, "Equalization techniques for multiple-valued data transmission and their application," Proc. 37th Int. Symp. Multiple-Valued Logic, 2007.

- [2] Y. Yuminaka and K. Yamamura, "Equalization techniques for multiple-valued data transmission and their application," Journal of Multiple-Valued Logic and Soft Computing, Vol.11, pp.569-582, 2007.

- [3] 山村 和義、弓仲 康史: "3次元積層チップ間誘導結合無線インタフェースを用いた多値信号伝送技術、'' 第 30 回多値論理 Forum、No. 6、2007.

- [4] 弓仲 康史、阿久津 正彦、吉田 幸弘、松村 泰成、坪田 雄介: "多値情報伝送における波形等化技術に関する考察、"多値論理とその応用研究会技術研究報告、MVL06、pp.46-52、2006.

- [5] T. Ezaki, K. Kondo, H. Ozaki, N. Sasaki, H. Yonemura, M. Kitano, S. Tanaka, and T. Hirayama, "A 160Gb/s Interface Design Configuration for Multichip LSI," IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp.140-141, 2004.

- [6] J. Burns, L. McIlrath, C. Keast, D. P. Vu, K. Warner, and P. Wyatt, "Three-Dimensional Integrated Circuits for Low-Power, High-Bandwidth Systems on a Chip," IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp.268-269, 2001.

- [7] N. Miura, D. Mizoguchi, M. Inoue, K. Niitsu, Y. Nakagawa, M. Tago, M. Fukaishi, T. Sakurai, and T. Kuroda, "A 1Tb/s 3W Inductive-Coupling Transceiver for 3D-Stacked Inter-Chip Clock and Data Link," IEEE Journal of Solid-State Circuits (JSSC), Vol.42, No.1, pp.111-122, 2007.

- [8] R. Sun, J. Park, F. O'Mahony, C. Yue, "A low-power, 20-Gb/s continuous-time adaptive passive equalizer," IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp.920-923, 2005.

# 〈発表資料〉

| 題 名                                         | 掲載誌・学会名等                         | 発表年月         |

|---------------------------------------------|----------------------------------|--------------|

| Equalization Techniques for Multiple-Valued | Journal of Multiple-Valued Logic | 2007年11月     |

| Data Transmission and Their Application     | & Soft Computing                 | 2001 + 11 /1 |

| Equalization Techniques for Multiple-Valued | IEEE Proc. 37h Int. Symp.        | 9007 Æ F 🖽   |

| Data Transmission and Their Application     | Multiple-Valued Logic            | 2007年5月      |

| Time-Domain Pre-Emphasis Techniques for     | IEEE Proc. 38th Int. Symp.       | 2008年5月      |

| Equalization of Multiple-Valued Data        | Multiple-Valued Logic            |              |

| High-Speed Data Transmission Techniques     | 17th International Workshop on   |              |

| using Raised Cosine Approximation           | Post-Binary ULSI Systems         | 2008年5月      |

| Signaling                                   |                                  |              |

| 3次元積層チップ間誘導結合無線インタフェースを                     | 30 回多値論理 Forum                   | 9007 Æ 7 H   |

| 用いた多値信号伝送技術                                 |                                  | 2007年7月      |

| 時間軸情報に着目した波形整形技術                            | 東北大学電気通信研究所講演会第                  |              |

|                                             | 55回ニューパラダイムコンピューティ               | 2007 年 9 月   |

|                                             | ング研究会                            | • • • •      |

| パルス幅変調プリエンファシスを用いた多値波形                      | 平成19年度電子情報通信学会東京                 | 9000 Æ 9 F   |

| 等化技術                                        | 支部学生会発表会                         | 2008年3月      |