# 光信号処理用全光シリアル-パラレル変換回路の研究

代表研究者 髙畑 清人 早稲田大学 大学院情報生産システム研究科 准教授

#### 1 はじめに

近年、タブレットやスマートホン等のモバイル端末が広く普及し、あらゆる場面で人々がネットワークにアクセスして、SNS、ネットショッピング、動画視聴等の様々なサービスを利用するようになっている。また、提供されるサービスも高精細動画に代表されるように、大容量のコンテンツが年々増加している。このため、データ通信トラフィックが急激に増加し続けており、通信ネットワークでは基幹系、メトロ系だけではなくアクセス系にも光ファイバ通信技術が広く導入されるようになった。リンク容量については、近年、デジタルコヒーレント光伝送技術やマルチキャリア伝送技術、マルチコアファイバ伝送技術の進展により飛躍的な増大が可能となった。一方で、ネットワークのノード系装置においては、信号処理の大部分を電子回路技術に依存しているため、スループット、遅延時間に加えて消費電力も大きな課題となっている。これらの問題を解決するために、光信号のままでルート、パケットの制御を行う技術の研究・開発が進められてきた。また、近年ではデータ・センター内のネットワークにおいても同様の課題が深刻になっており、その解決策として光信号処理技術が注目されている。

光パケットスイッチ・ネットワーク[1]におけるパケット・ラベル処理を高スループット、低遅延時間、低消費電力で行うために以下に挙げるような様々な光ラベル処理技術が報告されている。

- ・波長分割多重コードの利用 ([2] Q. Yang 他, 2001)

- ・表面反射型光スイッチの利用([3] R. Takahashi 他, 2003)

- ・光クロック動作トランジスタアレイの利用([4] R. Urata 他, 2006)

- ・半導体光増幅器による波長変換を利用 ([5] H. Hu 他, 2008)

- ・面発光型レーザーの偏波スイッチの利用([6] T. Katayama 他, 2013)

- ・マッハツエンダー遅延干渉計の利用 (「7] H. Kusano 他, 2015)

これらの中の多くが高速光シリアル信号を低速パラレル信号に変換してから信号処理を行う方法を提案しており、光シリアルーパラレル変換器が重要な構成要素となっている。しかしながら、多くの光シリアルーパラレル変換器は高速シリアル信号をパラレル展開する際にビット間隔に応じて段階的に遅延長を変えた光遅延線をビット数分備える構成を用いており、この光遅延線が光シリアルーパラレル変換器全体のサイズ小型化を阻害する要因となっている。本研究では、この問題を解決するために、シリコンフォトニクス技術に基づいた新しい小型光遅延ユニットを提案し、その基礎検討と基本設計を実施する。

#### 2 新たな光シリアル-パラレル変換回路構成法の提案

#### 2-1 従来の光シリアル-パラレル変換回路構成法

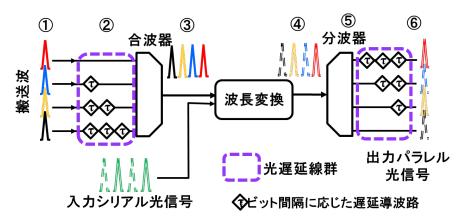

図1に波長変換技術を応用した光シリアルーパラレル変換回路[5]の構成を示す。この光回路は波長による分波を用いて入力光シリアル信号のパラレル展開を達成する方法を用いているため、まず単一波長で伝送されてきた光シリアル信号をビット毎に異なる波長に置換した後に、波長分波器に入力している。以下に、この回路による光シリアルーパラレル変換動作を順に説明する。

- ① 波長の異なる搬送波パルスをビット数に応じて用意。(光周波数コム技術[8]、スペクトルスライス技術[9]等により生成。)

- ② これらの波長の異なる複数の搬送波をビット間隔に応じた伝搬遅延時間  $(\tau)$  を段階的に与える遅延 光導波路を通過させることでパルスに時間差を生じさせる。

- ③ ②のパルス群を波長合波器によって同一導波路上に集約し、シリアル搬送波パルス列に変換する。

- ④ ③の搬送波パルス列と入力シリアル光信号を半導体光増幅器に同時に入力し、相互利得変調、或いは相互位相変調により入力信号の情報を搬送波パルス列に乗せる。(波長変換)

- ⑤ 得られたビット毎に波長の異なるシリアル光信号を波長分波器を用いて波長毎に異なる出力ポートに 導波させる。

⑥ ⑤で分離されたパルスをビット間隔に応じた伝搬遅延時間  $(\tau)$  を段階的に与える遅延光導波路を通過させることでパルスのタイミングを揃え、パラレル光信号を得る。

図1 従来の光シリアルーパラレル変換回路構成法

図1にも明確に示されているように、この構成では、ビットパルス毎に異なる個別の光遅延導波路から成る 光遅延線群を2セット用いており、これらを光ファイバで構成する場合はもちろんのこと、平面光導波路で 構成する場合においてもこの多数の光遅延導波路の存在が光シリアル-パラレル変換器全体のサイズ小型化 の阻害要因となる。

#### 2-2 小型光シリアル-パラレル変換回路構成法の提案

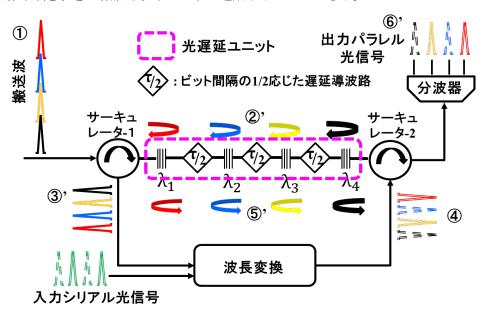

前項で述べた遅延光線群のサイズの問題を解決するために、図2に示す新しい小型光シリアルーパラレル変換回路を提案する。本提案回路ではシリアルーパラレル変換の基本的な動作原理は図1の回路と同じであるが、多数の遅延光導波路を1つの小型光遅延ユニットで置き換えることで回路全体のサイズを飛躍的に小型化することを図る。提案する小型光遅延ユニットは搬送波の各波長に応じた反射帯域を持つ複数の回折格子をビット間隔の半分( $\tau$ /2)に対応する遅延光導波路で直線状に接続した簡易な構成である。本ユニットにより前項で示した動作手順②、③の機能を以下のように達成することができる。

図2 提案する光シリアルーパラレル変換回路構成法

② 波長の異なる複数の搬送波パルスをサーキュレータ-1 を介して光遅延ユニットに入力する。搬送波パルスは各々が波長に応じた回折格子で反射される。

③'搬送波パルスはサーキュレータ-1 を介して光遅延ユニットから出力される。この際に波長毎にサーキュレータ-1 と回折格子の間を往復する伝搬距離が異なるため、ユニットからの出力はシリアル搬送波パルス列となる。

従来回路と同様に波長変換によって入力シリアル光信号の情報を搬送波パルス列に乗せた後に、本ユニットにより前項で示した動作手順⑤、⑥の機能を以下のように達成する。

- ⑤'ビット毎に波長の異なるシリアル光信号をサーキュレータ-2を介して②'とは逆側のポートから光遅延ユニットに入力する。シリアル光信号パルスは各々が波長に応じた回折格子で反射され、サーキュレータ-2を介して光遅延ユニットから出力される。この際に波長毎にサーキュレータ-2と回折格子の間を往復する伝搬距離が異なり、ユニットからは波長の異なる全パルスが同一のタイミングで出力される。

- ⑥'これら全パルスを波長分波器を用いて波長毎に異なる出力ポートに導波させることで、パラレル光信 号を得る。

本提案構成では直線状に配列された遅延光導波路を波長の異なる全ての光パルスで共用するため、パルス毎に個別の遅延光導波路が必要となる従来構成と比較して、回路全体の大幅な小型化が可能となる。また、光遅延ユニットを双方向(③'と⑤'で各パルスは逆方向から光遅延ユニットに入力される)で用いているため、③'で生じたパルス間の遅延差が⑤'で完全に相殺され、出力パラレル信号のタイミングを高精度で揃えることが可能となるという長所も併せ持っている。

#### 3 回路の設計と考察

#### 3-1 小型光遅延ユニットの基本設計

図2に示した光シリアルーパラレル変換回路においては、小型光遅延ユニットが新しく提案するキー部品である。本研究では、主に小型化の観点から、非屈折率差( $\Delta$ n)が大きく曲線光導波路の曲率半径を小さくすることが可能な SOI(Silicon on Insulator)光導波路での作製を仮定して設計に取り組んだ。シリコンフォトニクス技術を用いることは、低コスト化の点においても有利である。また、設計検討を開始するにあたっては、ターゲットとする機能(信号レート、ビット数)を定義する必要がある。今回の検討では、入力信号を 40 Gbit/s シリアル光信号とし、それを 8 ビットのパラレル光信号に変換して出力する機能を目標として設定した。

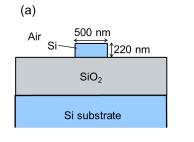

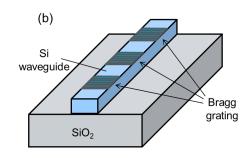

光導波路構造は単一モード SOI 光導波路として標準的な幅 500 nm、高さ 220 nm の Si 導波路とした(図 3 (a))。光遅延ユニットは、図 3 (b)に示すように、信号のビット間隔に対応する一定の間隔で反射波長の異なる回折格子を光導波路上に配列する構造である。

図2に色分けして示されているように、波長の異なる光は各々の波長に対応した回折格子で反射されて入力端で見まるために、8ビット、即ち8つの波計を行った。回折格子は導波路幅方向に凹凸を形成(導波路壁面に凹凸を形成)する構造とした。設

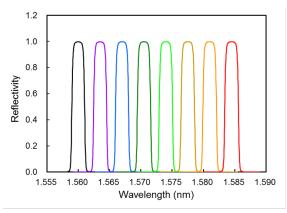

図3 SOI 光導波路の構造 (a) 断面図 (b) 光遅延線と回折格子

計にあたっては、反射波長を明確に分離するためには隣接波長間での反射スペクトルの重なりを可能な限り低減する必要がある。まず、図 4 (a) に示す通常の均一構造回折格子で設計したところ、十分な反射率を得ようとすると図 4 (b) に示すように反射スペクトルのサイドローブが無視できないレベルとなり、波長分離特性の劣化を招く結果であった。そこで、サイドローブを低減するために回折格子に図 4 (c) に示すアポダイズ構造を導入し、改善を図った。その結果、図 4 (d) のようにサイドローブのない反射スペクトルが得られた。シミュレーションにより得られた光遅延ユニット (8 つの回折格子を含む) の反射特性を図 5 に示す。波長 1560 nm から 1584.5 nm まで波長間隔 3.5 nm で 8 つの反射帯を設計した。8 つすべての回折格子は長さ 900  $\mu$ m で設計し、中心波長での反射率 99%以上、反射帯域(1 dB 低下帯域)1.8 nm が得られている。隣接する波長帯

も含め他の波長帯ではほぼ反射のない特性を有することを示している。

図5 光遅延ユニットの反射特性

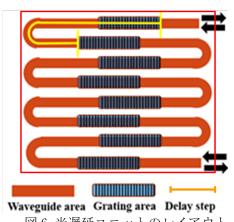

図6 光遅延ユニットのレイアウト

#### 3-2 小型光遅延ユニットのレイアウト設計

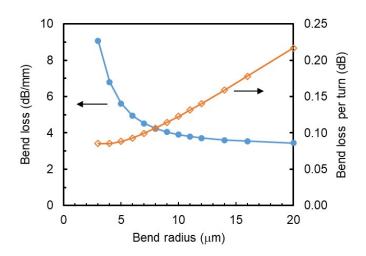

本光遅延ユニット反射を利用しているため 40 Gbit/s 信号のビット間隔 25 ps を得るため には、光遅延線の長さとしては片道 12.5 ps に 対応する遅延長が必要となる。これより、回折 格子中心間の間隔は1924 µm となり、その結果 光遅延ユニット全体の導波路長は 15.386 mm と なった。このような長尺の導波路を比較的小さ いチップ面積に収めるために、光遅延ユニット のレイアウトには図6に示す折り畳み型を採用 した。占有面積低減のためには、導波路の曲げ 半径を小さくする必要があるが、光パワー損失 も考慮する必要がある。曲げ半径と曲げ損失、 及び 180 度折り返しで生じる損失の関係を計算 により求めた結果を図7に示す。この結果から、 曲げ半径を6 µm に設定した。この値を用いて光

SOI 光導波路の曲げ半径と曲げ損失

遅延ユニットのレイアウト設計を行った結果、専有面積としては1917×84 μm<sup>2</sup>と求められた。

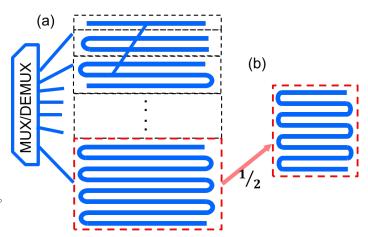

小型化の効果を検証するために、同一の S0I 光導波路を用いて従来構成の光遅延線を設計した場合との専有面積の比較を行った。図 8 (a) に示すように、従来構成の場合は、ビット間隔に応じた伝搬遅延時間 ( $\tau$ )を段階的に与える遅延光導波路をビット数分用意する必要がある。40 Gbit/s 信号のビット間隔 25 ps を得るためには遅延線長として 3848  $\mu$ m が必要となり、8 ビットの場合の最も長い遅延線の専有面積は上記と同じ曲げ半径 6  $\mu$ m で折り畳み型を用いたとして 3841×84  $\mu$ m²となり、この部分だけでも図 8 (b) に示す小型光遅延ユニットの約 2 倍となる。更に、8 ビット分すべての遅延線の専有面積は小型光遅延ユニットの約 8 倍

となる。また、図1に示すように従来の光シリ アルーパラレル変換回路構成法では光遅延線群 を2つ使用しているが、図2に示すように本提 案構成では単一の光遅延ユニットを双方向から 使用することで部品点数の削減を図っている。 この点も考慮すると、本小型光遅延ユニットは 従来構成に比べて光遅延部分の専有面積を 1/16 に小型化することができると評価される。 更に、本小型光遅延ユニットは光合波器/分波器 の機能も有しているため、光合波器/分波器が不 要となり、この点においても光シリアルーパラレ ル変換回路全体の小型化への寄与が期待される。 但し、この点については、提案する小型光シリ アルーパラレル変換回路は従来構成法では用 いていないサーキュレータを2つ使用する構 成となっているので、光合波器/分波器とサー キュレータのサイズを考慮して論じる必要が ある。

図8 光遅延線のサイズ比較

(a) 従来の遅延線構成(b) 小型光遅延ユニット

#### 4 まとめ

光パケットのラベル処理等の光信号処理において重要な役割を担う光シリアルーパラレル変換回路について、その主要構成部品である光遅延線の小型化を主目的として研究を行った。従来の光シリアルーパラレル変換回路構成法ではビット間隔に応じた遅延時間の分だけ段階的に長さを調整したビット数分の光遅延線が必要であり、これが回路全体の小型化の阻害要因となっているため、多数の光遅延線が不要となる新たな小型光遅延ユニットを提案・設計した。提案した小型ユニットは、ビット数(波長数)に応じた複数のブラッグ回折格子を Si 基板上 SOI 光導波路に直列に配置した構成であり、同一の遅延光導波路を複数ビットで共用可能、光の反射を用いているため必要な遅延導波路長が 1/2 となる、双方向入力で用いることで単一の遅延ユニットを 2 回使用可能、という小型化に適した多くの長所を有しており、光シリアルーパラレル変換回路で用いられる光遅延線の専有面積を従来比で約 1/16 に小型化がかのうであることをレイアウト設計で確認した。シリアルーパラレル変換動作についてはシミュレーションによる検証を継続中である。

本研究で得られた新しい構成法に基づく小型光遅延ユニットの基本設計に関する成果を、国際会議で報告した。

本研究によって、光遅延線と光合波器/分波器の両方の機能を併せ持つ新しい小型光遅延ユニットの実現に向けた有益な知見が得られた。

### 【参考文献】

- [1] A. Takada and P. H. Jin, "Architecture of ultrafast optical packet switching ring network," IEEE J. Lightwave Technol., vol. 20, pp. 2306-2315, Dec. 2002.

- [2] Q. Yang, et al, "WDM packet routing for high-capacity data networks," J. Lightw. Technol., vol. 19, no. 10, pp. 1420–1426, 2001.

- [3] R. Takahashi et al., "1-Tb/s 16-b all-optical serial-to-parallel conversion using a surface-reflection optical switch," IEEE Photon. Technol. Lett., vol. 5, no. 2, pp. 287–289, 2003.

- [4] R. Urata et al., "An optically clocked transistor array with dual serial-to-parallel and parallel-to-serial conversion capability for optical label swapping," IEEE Photon. Technol. Lett., vol. 18, no. 1, pp. 67–69, 2006.

- [5] H. Hu et al., "40-Gb/s All-Optical Serial-to-Parallel Conversion Based on a Single SOA," IEEE Photon. Technol. Lett., vol. 20, no. 13, pp. 1181–1183, 2013.

- [6] T. Katayama et al., "All-optical header recognition and packet switching using polarization bistable VCSEL," IEEE Photon. Technol. Lett., vol. 25, no. 9, pp. 802–805, 2013.

- [7] H. Kusano et al., "Investigation of a Silicon Photonic Optical Serial-to-Parallel Converter with Mach–Zehnder Delay Interferometers and Integrated Ge-PDs," IEEE J. Quantum Electron., vol. 51, no. 8, 6300109, 2015.

- [8] P. M. Anandarajah et al., "Flexible optical comb source for super channel systems," Proc. of 2013 Optical Fiber Communication Conference (OFC), Oth3I.8, 2013.

- [9] Q. Hu et al., "Optimum Linewidth of Spectrum-Sliced Incoherent Light Source Using a Gain-Saturated Semiconductor Optical Amplifier," J. Lightw. Technol., vol. 33, no. 17, pp. 3744–3450, 2015.

## 〈発表資料〉

| 題名                                                                         | 掲載誌・学会名等                                               | 発表年月        |

|----------------------------------------------------------------------------|--------------------------------------------------------|-------------|

| "A waveguide-based bidirectional optical delay unit with Bragg reflectors" | Asia Communications and Photonics Conference (ACP2019) | 2019 年 11 月 |

|                                                                            |                                                        |             |

|                                                                            |                                                        |             |